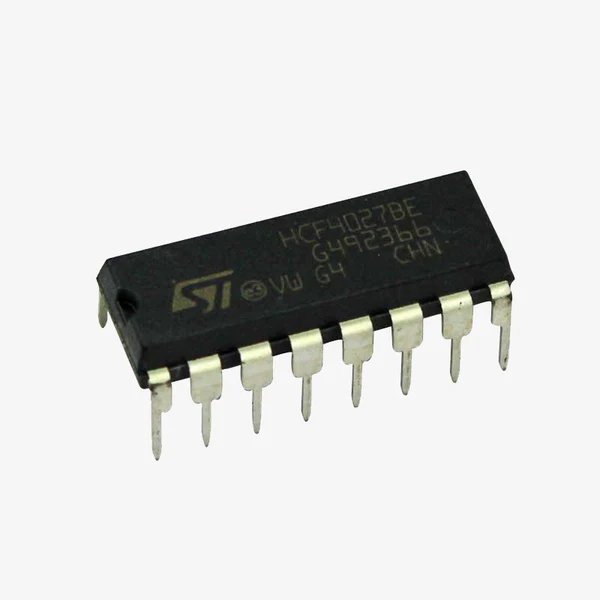

CD4027 Flip Flop JK Master Slave Doble

[CD4027] CD4027 Flip Flop JK Master Slave Doble

Referencia Interna:

CD4027

Flip-Flop Dual J-K Maestro-Esclavo - CD4027

El CD4027 es un circuito integrado CMOS que contiene dos flip-flops J-K de tipo maestro-esclavo, los cuales son de los más versátiles en lógica secuencial. Cada flip-flop tiene entradas J, K, Set, Reset y Reloj, junto con salidas Q y Q-negada. A diferencia del flip-flop tipo D, el J-K puede mantener su estado, ponerse a '1', a '0' o conmutar (toggle) su salida, dependiendo de los valores en J y K. Esta flexibilidad lo hace ideal para diseñar contadores síncronos, registros de desplazamiento y máquinas de estado complejas, donde se requiere un control preciso sobre el comportamiento del estado.

Especificaciones Técnicas

| Tipo de dispositivo | Flip-Flop dual J-K Maestro-Esclavo |

|---|---|

| Familia lógica | CMOS Serie 4000 |

| Voltaje de alimentación (VDD) | 3 V a 18 V |

| Número de flip-flops | 2 (independientes) |

| Modos de operación | Set, Reset, Mantener, Conmutar (Toggle) |

| Entradas asíncronas | Set y Reset (activas en alto) |

| Frecuencia máxima de reloj | 8 MHz típico @ 10V |

| Número de pines | 16 (DIP-16) |

| Tiempo de propagación (CLK a Q) | 125 ns típico @ 10V |

| Encapsulado disponible | DIP-16, SOIC-16, TSSOP-16 |

| Rango de temperatura de operación | -55 °C a 125 °C (industrial) |

| Tiempo de Set-up | 50 ns típico @ 10V |

| Corriente de reposo típica | 20 nA @ 5V |

Consultar ficha técnica (Datasheet)

Descarga la hoja de datos del CD4027 con sus características clave.

Descargue su Datasheet (PDF)