74LS189 Memoria RAM de 64 Bits Circuito TTL

[74LS189] 74LS189 Memoria RAM de 64 Bits Circuito TTL

Referencia Interna:

74LS189

Circuito Integrado 74LS189 - Decodificador/Demultiplexor de 1 de 32 Líneas

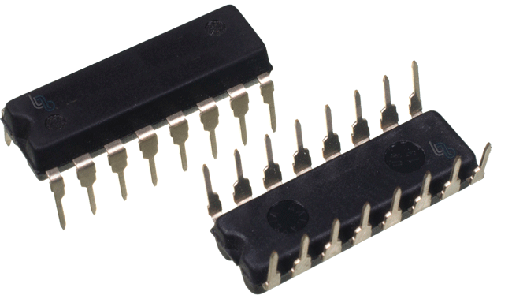

El 74LS189 es un circuito integrado de la familia TTL LS que implementa un decodificador/demultiplexor de 5 bits de dirección a 32 salidas, con entradas de habilitación y salidas invertidas. Diseñado para selección de memoria y distribución de señales, permite la activación individual de 32 líneas a partir de un código binario de 5 bits. Su bajo consumo de potencia, tiempos de respuesta rápidos y precisión hacen que sea ideal para direccionamiento de memoria, control de periféricos, multiplexación y aplicaciones de decodificación en sistemas digitales. Fabricado en encapsulado DIP-16 (también disponible en SOIC-16), funciona con 5 V y opera con fiabilidad en rangos comerciales de temperatura, siendo ampliamente utilizado en prototipos, sistemas embebidos y diseños de control industrial.

Especificaciones Técnicas

| Tipo de dispositivo | Decodificador/demultiplexor de 5:32 (salidas invertidas) |

|---|---|

| Familia lógica | 74LS TTL (Low Power Schottky) |

| Voltaje de alimentación nominal | 5 V (rango: 4.75 V a 5.25 V) |

| Corriente de consumo típica | 16 mA |

| Número de pines | 16 (DIP-16) |

| Tiempo de propagación (tpd) | 25 ns máximo (entrada → salida) |

| Ancho de pulso mínimo (tw) | 10 ns |

| Ancho de pulso máximo | No aplica (lógica combinacional) |

| Encapsulado disponible | DIP-16, SOIC-16 |

| Rango de temperatura de operación | 0 °C a 70 °C (comercial) |

| Disipación de potencia típica | 80 mW |

| Compatibilidad TTL/CMOS | Salida open-collector compatible con TTL |

| Fan-out (carga de salida) | 15 entradas TTL LS estándar |

| Entrada de trigger | 5 bits de dirección con habilitación |

Consultar ficha técnica (Datasheet)

Descarga la hoja de datos del 74LS189 con sus características clave.

Descargue su Datasheet (PDF)