74LS17 Flip Flop Tipo D x 6 con Clear, Circuito TTL

[74LS17] 74LS17 Flip Flop Tipo D x 6 con Clear, Circuito TTL

Referencia Interna:

74LS17

Circuito Integrado 74LS17 - Buffers Hexagonales con Trigger Schmitt

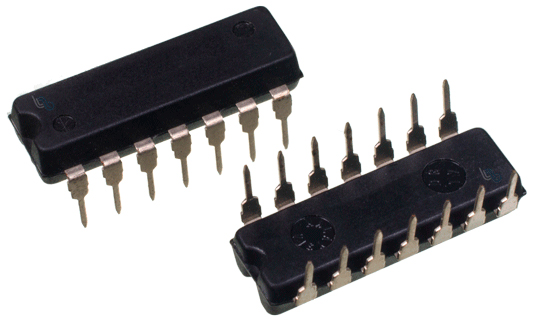

El 74LS17 es un circuito integrado de la familia TTL LS que contiene seis buffers lógicos no inversores con entradas de trigger Schmitt para mejora de señal. Diseñado para filtrado de ruido y buffering, permite la conversión de señales lentas o ruidosas en transiciones limpias. Su bajo consumo de potencia, tiempos de respuesta rápidos y precisión hacen que sea ideal para debouncing, osciladores, interfaces de sensores y aplicaciones de lógica en entornos ruidosos en sistemas digitales. Fabricado en encapsulado DIP-14 (también disponible en SOIC-14), funciona con 5 V y opera con fiabilidad en rangos comerciales de temperatura, siendo ampliamente utilizado en prototipos, sistemas embebidos y diseños de control industrial.

Especificaciones Técnicas

| Tipo de dispositivo | Buffers hexagonales con Schmitt trigger |

|---|---|

| Familia lógica | 74LS TTL (Low Power Schottky) |

| Voltaje de alimentación nominal | 5 V (rango: 4.75 V a 5.25 V) |

| Corriente de consumo típica | 10 mA |

| Número de pines | 14 (DIP-14) |

| Tiempo de propagación (tpd) | 16 ns máximo (entrada → salida) |

| Ancho de pulso mínimo (tw) | 5 ns |

| Ancho de pulso máximo | No aplica (lógica combinacional) |

| Encapsulado disponible | DIP-14, SOIC-14 |

| Rango de temperatura de operación | 0 °C a 70 °C (comercial) |

| Disipación de potencia típica | 50 mW |

| Compatibilidad TTL/CMOS | Salida y niveles compatibles con familias TTL estándar |

| Fan-out (carga de salida) | 10 entradas TTL LS estándar |

| Entrada de trigger | 1 entrada con Schmitt trigger por buffer |

Consultar ficha técnica (Datasheet)

Descarga la hoja de datos del 74LS17 con sus características clave.

Descargue su Datasheet (PDF)