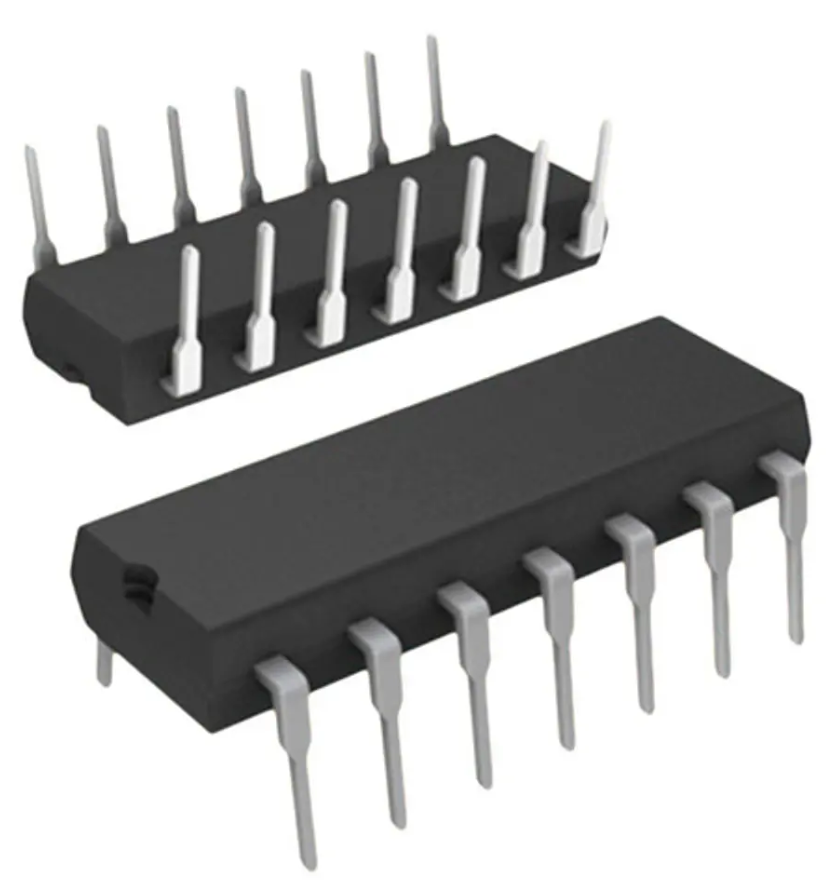

74HC125 Buffer Cuádruple CMOS Triestado DIP14

[74HC125] 74HC125 Buffer Cuádruple CMOS Triestado DIP14

Referencia Interna:

74HC125

Circuito Integrado 74HC125 - Buffers de Bus Cuádruples con Salida 3-STATE

El 74HC125 es un circuito integrado de la familia CMOS de alta velocidad (HC) que contiene cuatro buffers no inversores con salidas de tres estados (3-STATE). Cada buffer tiene una entrada de habilitación (enable) independiente y activa en bajo, lo que permite controlar si la salida está activa o en estado de alta impedancia. Esta característica es esencial para sistemas con buses compartidos, donde múltiples dispositivos necesitan conectarse a la misma línea sin causar conflictos. Es ideal para drivers de bus, aislamiento de circuitos y expansión de puertos de E/S.

Especificaciones Técnicas

| Tipo de dispositivo | Buffers cuádruples no inversores con salidas 3-STATE |

|---|---|

| Familia lógica | 74HC (High-Speed CMOS) |

| Voltaje de alimentación nominal | 2 V a 6 V |

| Corriente de consumo típica | 1 µA (en reposo) |

| Número de pines | 14 (DIP-14) |

| Tiempo de propagación (tpd) | 10 ns típico (a 5 V) |

| Ancho de pulso mínimo (tw) | No aplica (lógica combinacional) |

| Ancho de pulso máximo | No aplica (lógica combinacional) |

| Encapsulado disponible | DIP-14, SOIC-14, SSOP-14 |

| Rango de temperatura de operación | -40 °C a 85 °C (estándar) |

| Disipación de potencia típica | |

| Compatibilidad TTL/CMOS | Entradas y salidas compatibles con niveles CMOS y TTL |

| Fan-out (carga de salida) | 15 cargas LSTTL o múltiples cargas HC |

| Entrada de trigger | Habilitación activa en bajo (OE) por buffer |

Consultar ficha técnica (Datasheet)

Descarga la hoja de datos del 74HC125 con sus características clave.

Descargue su Datasheet (PDF)